# Klausur zur Vorlesung Schaltungstechnik

## TU Berlin, Sommersemester 2013, 24.07.2013

Bearbeitungszeit: 3 Stunden

| Name (Nachname, Vorname):          | Aufgabe:      | Punkte: |

|------------------------------------|---------------|---------|

| MatrNr.:                           | 1 1 1         | / 28    |

| < ×                                | 2             | / 22    |

| Studiengang:                       | 3             | / 40    |

| BSc / MSc / Diplom:                | 4             | / 20    |

|                                    | 5             | /10     |

| Erasmus- oder Gast-Student/in:  Ja | Gesamt:       | / 120   |

|                                    |               |         |

| Note: Datum:                       | Unterschrift: |         |

Bitte füllen Sie auf dieser Seite nur die weißen Felder aus.

Füllen Sie bitte ebenso auf allen abgegebenen Seite jeweils die Kopfzeile aus und verwenden Sie nur dieses Papier für die Lösung der Aufgaben.

Viel Glück!

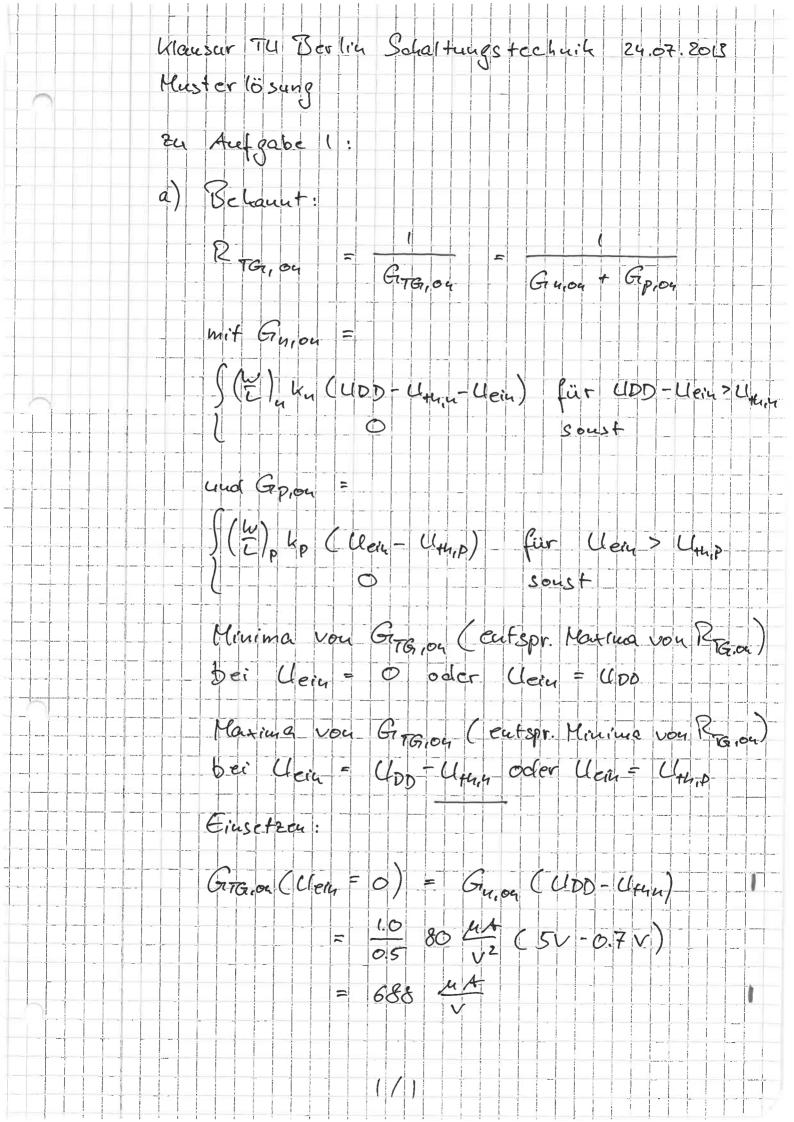

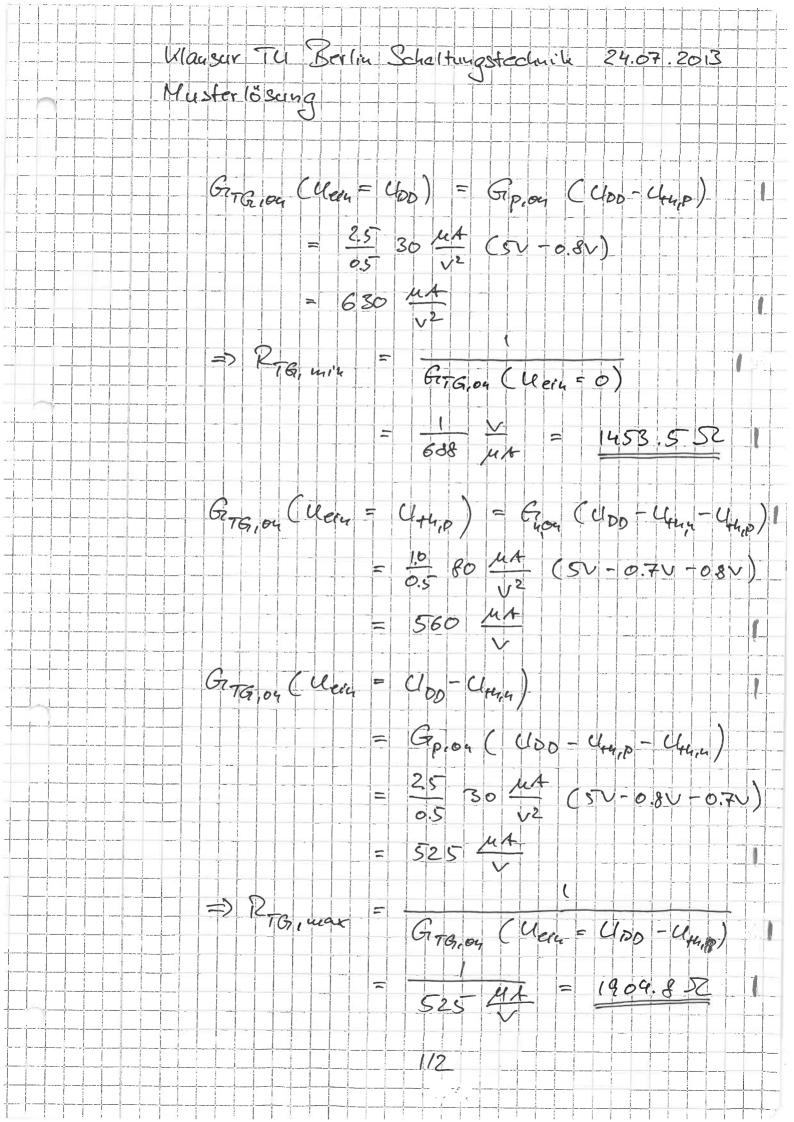

#### Aufgabe 1:

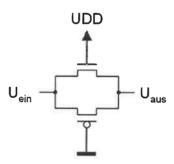

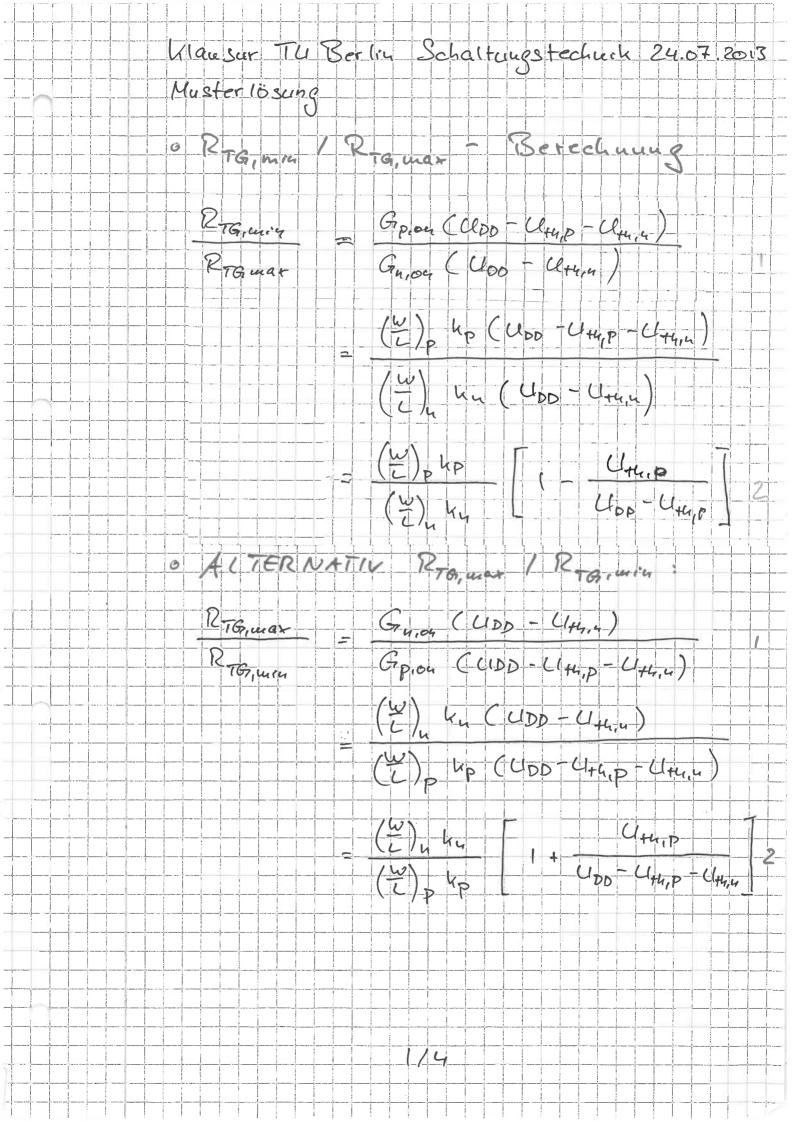

Gegeben ist ein Transmission-Gate in 0.5  $\mu$ m CMOS-Technologie mit  $L=L_{min}=0.5$   $\mu$ m,  $W_n=1.0$   $\mu$ m,  $W_p=2.5$   $\mu$ m,  $k_n=80$   $\mu$ A/V<sup>2</sup>,  $k_p=30$   $\mu$ A/V<sup>2</sup>,  $U_{th,n}=700$  mV,  $U_{th,p}=800$  mV. Der Spannungsabfall zwischen Drain und Source kann als sehr klein angenommen werden.

- a) Berechnen Sie den minimalen und den maximalen Widerstand des Transmission-Gates für 12 UDD = 5 V und  $U_{ein} = 0 \dots UDD$ .

- b) Wie gering darf UDD minimal werden, damit für zu schaltende Signale zwischen 0 und UDD 4 der maximale Widerstand 10 kΩ nicht überschreitet?

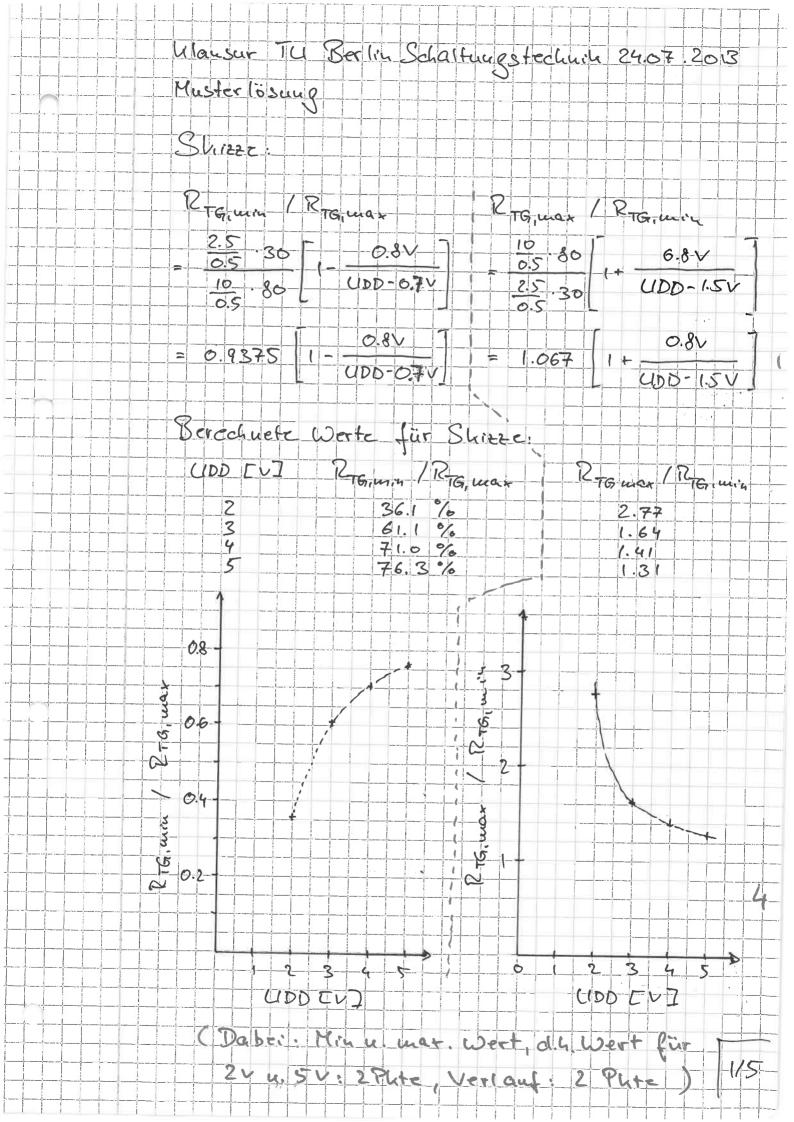

- c) Berechnen Sie das Verhältnis aus minimalem zu maximalen Widerstand des Transmission-Gates innerhalb des Bereiches  $U_{ein}=0$  ... UDD als Funktion von UDD für UDD=2.0 ... 5.0 V. (Formel) Skizzieren Sie auch (quantitativ!) das oben berechnete Verhältnis aus maximalem zu minimalem Widerstand des Transmission-Gates innerhalb des Bereiches  $U_{ein}=0$  ... UDD als Funktion von UDD für UDD=2.0 ... 5.0 V.

- d) Welche Weite  $W_p$  müsste der pMOS Transistor haben, damit bei der oben gegebenen Weite des nMOS-Transistors und UDD = 1.8 V der Widerstand für  $U_{ein} = 0$  und für  $U_{ein} = UDD$  identisch sind? Geben Sie einen auf 0.1  $\mu$ m gerundeten Wert an.

Summe: 28

Hinweis: Für die analytischen Betrachtungen/Berechnungen ist der Weg über die Betrachtung des Leitwertes des Transmission-Gates in einigen Teilaufgaben rechentechnisch ggf. der einfachere Ansatz.

Abbildung zu Aufgabe 1. Die Abbildung zeigt die an den Gates der Transistoren angelegten Spannungspegel für den eingeschalteten Zustand.

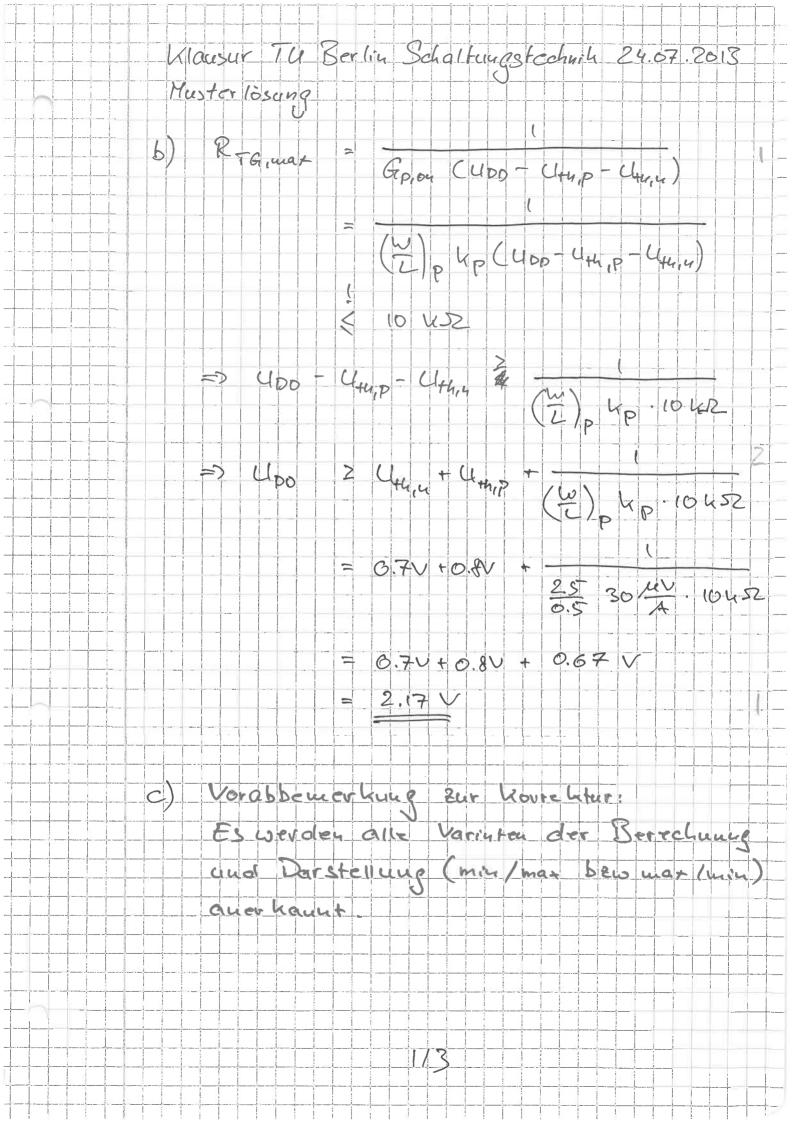

#### Aufgabe 2:

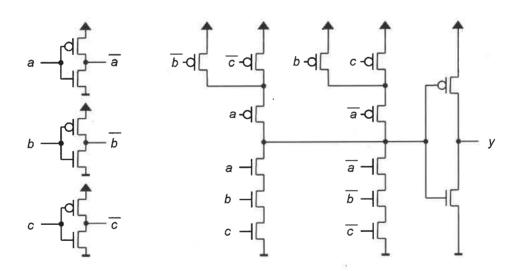

Gegeben ist die unten angegebene Schaltung, die eine optimierte Implementierung einer logischen Verknüpfung realisiert.

- a) Geben Sie eine Wahrheitstabelle für die Ausgangsvariable y als Funktion der 4 Eingangsvariablen a, b und c an.

(Anmerkung: Jede mögliche Kombination der Eingangsvariablen führt zu definierten Ausgangszuständen.)

- b) Ermitteln Sie aus der Tabelle aus a) oder (besser / einfacher!) durch Betrachtung der Pull-Down- oder Pull-Up-Pfade den logischen Ausdruck, den diese Schaltung realisiert. Geben Sie die Funktion v in möglichst einfacher Form an.

- c) Setzen Sie diese Funktion ausschließlich mit NAND-Gattern mit zwei Eingängen und 8 Invertern um und skizzieren Sie die sich ergebende Schaltung.

- d) Wie viele MOS-Transistoren enthält Ihre in c) skizzierte Schaltung (kurze Begründung oder 2 Angabe der Transistoranzahl pro Gatter in c)).

- e) Setzen Sie die ermittelte Funktion nun auch ausschließlich mit NOR-Gattern mit beliebig 4 vielen Eingängen und Invertern um und skizzieren Sie die sich ergebende Schaltung.

Summe: 22

Abbildung zu Aufgabe 2.

#### Aufgabe 3:

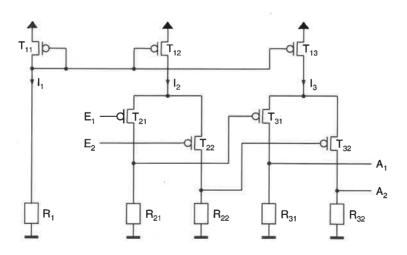

Die unten gegebene Abbildung zeigt einen einfachen Differenzverstärker mit differentiellem Ausgang und weiteren Elementen zur Einstellung des Arbeitspunktes der Schaltung. Die Betriebsspannung UDD beträgt 3.3 V. Technologie- bzw. Transistorkenngrößen sind  $L_{min}=0.35~\mu\text{m}$ ,  $k_p=56~\mu\text{A}$  /  $V^2$ ,  $U_{th,p}=0.7~\text{V}$ . Alle Transistoren haben eine Kanallänge  $L=0.7~\mu\text{m}$ . Alle Transistoren werden mit einer effektiven Gatespannung von 250 mV betrieben.

- a) Identifizieren und benennen Sie bekannte Teilschaltungen möglichst genau.

- b) Ausgang A1 wird (willkürlich) als nicht-invertierender Ausgang der Schaltung festgelegt. 4 Welches ist unter dieser Bedingung der invertierende, welches der nicht-invertierende Eingang der Schaltung (Begründung Sie Ihre Aussage dadurch, dass Sie an *jedem* signalführenden Knoten in der Schaltung Pfeilsymbole eintragen; ohne Begründung oder Skizze keine Punkte).

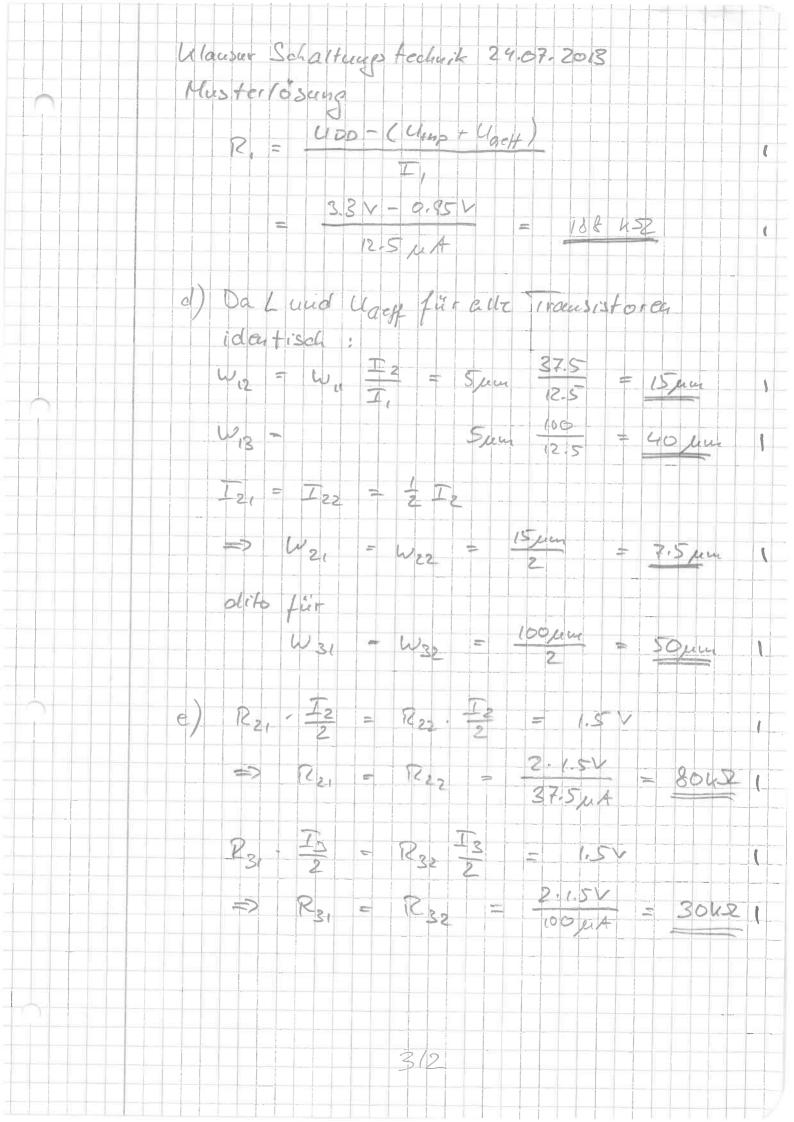

- c) Der Strom I<sub>1</sub> soll 12.5 μA betragen. Bestimmen Sie die Weite von T<sub>11</sub> und den Wert des Widerstandes R<sub>1</sub>. Hinweis: Verwenden Sie bei der Berechnung des Transistorstromes eine N\u00e4herungsformel, d.h., vernachl\u00e4ssigen Sie den \u00fcber den Parameter \u00e2 modellierten Effekt der Kanall\u00e4ngenmodulation.

- d) Dimensionieren Sie die Weiten von  $T_{12}$  und  $T_{13}$  so, dass die entsprechenden Ströme  $I_2=37.5~\mu\text{A}$  und  $I_3=100~\mu\text{A}$  betragen. Dimensionieren Sie die ferner die Weiten aller übrigen Transistoren ( $T_{21},\,T_{22},\,T_{31},\,T_{32}$ ).

- e) Dimensionieren Sie die Werte aller verbleibenden Widerstände derart, dass die Gleichtakt- (oder Common-Mode-) Ausgangsspannung beider Verstärkungsstufen je 1.5 V beträgt.

- f) Geben Sie die minimale und die maximale Gleichtakt- (oder Common-Mode-) 6 Eingangsspannung an unter der Bedingung, dass alle Transistoren im Sättigungsbereich betrieben werden. Geben Sie dazu jeweils eine kurze Skizze (oder Erklärung) und die entsprechenden Spannungswerte an.

- g) Zeichnen Sie ein Kleinsignal-Ersatzschaltbild der Schaltung, mittels dessen Sie Kleinsignal-Verstärkung der Schaltung etc. herleiten könnten. Reduzieren Sie dieses Ersatzschaltbild auf die relevanten Elemente, d.h., vereinfachen Sie dieses Ersatzschaltbild so weit wie möglich.

- h) Geben Sie die Kleinsignal-Spannungsverstärkung der gesamten Schaltung an (Formel und 8 Wert).

Hinweis: Berechnen Sie diese bzw. geben Sie diese vorzugsweise an mit Hilfe bekannter Näherungs-Formeln, d.h. Verwendung der Ergebnisse aus Aufgabenteil g) ist zwar möglich, aber nicht erforderlich.

Summe: 40

4

Abbildung zu Aufgabe 3

#### Aufgabe 4:

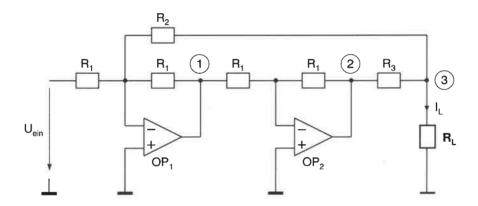

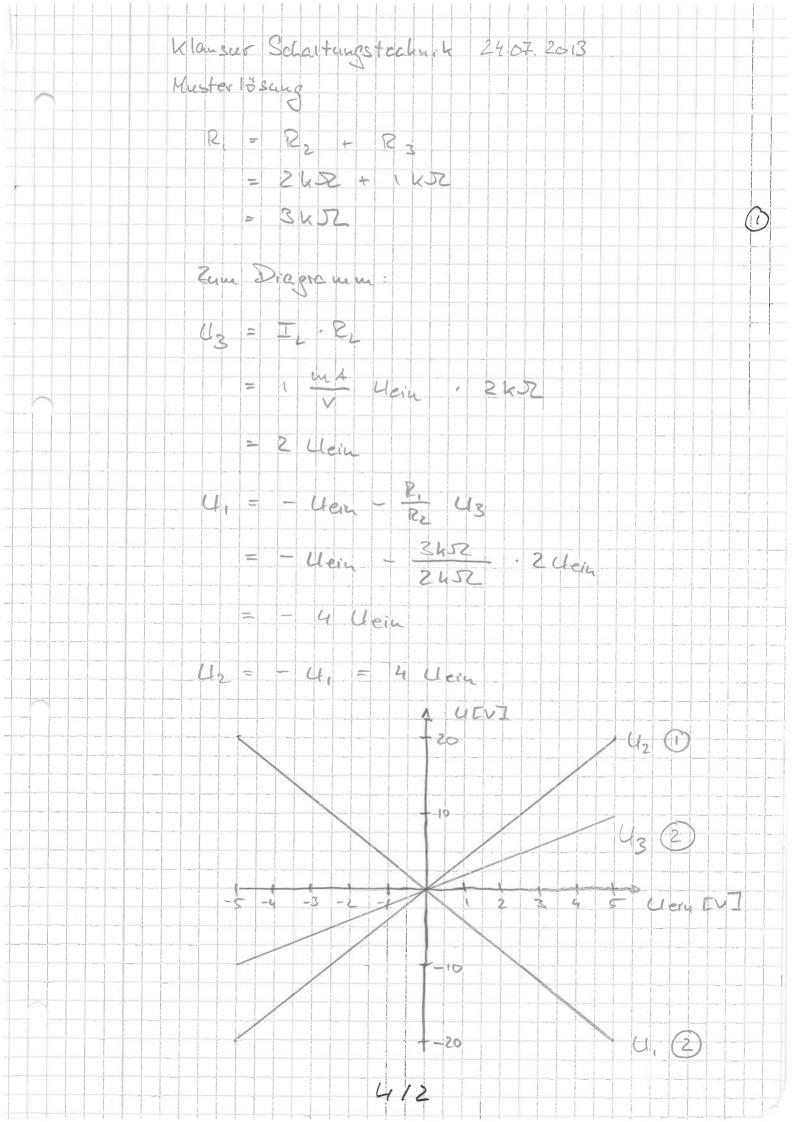

Die unten stehende Abbildung zeigt eine Schaltung, die bei richtiger Dimensionierung eine spannungsgesteuerte Stromquelle darstellt, d.h., der Strom  $I_L$  durch das Lastelement ist nur eine Funktion der Eingangsspannung  $U_{ein}$  und hängt nicht vom Wert  $R_L$  des Lastwiderstandes ab.

Diese Schaltung soll im Folgenden schrittweise analysiert und dimensioniert werden. Für diese Analyse sind interne Knoten der Schaltung mit den Ziffern 1, 2, 3 gekennzeichnet, die entsprechenden Spannungen an diesen Konten werden mit  $U_1$ ,  $U_2$  und  $U_3$  bezeichnet.

Hinweis: Beide Operationsverstärker werden als Verstärker, d.h. NICHT als Komparatoren betrieben.

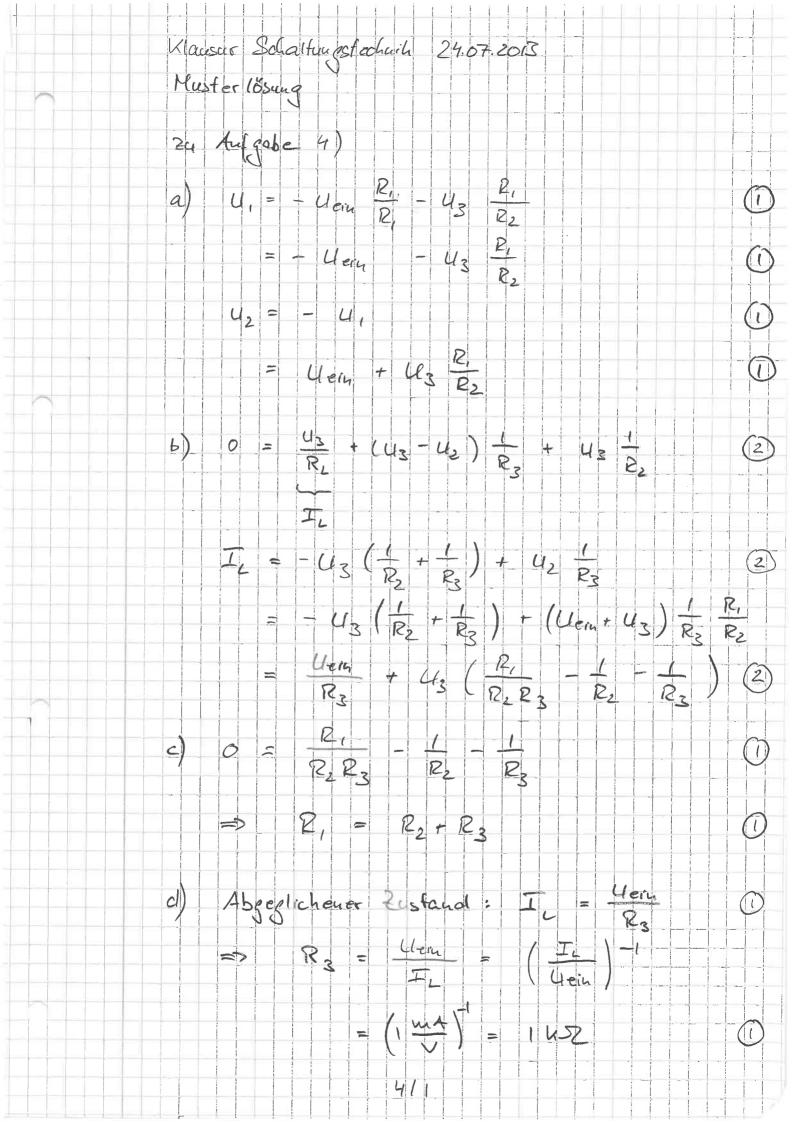

- a) Geben Sie zunächst  $U_1$  als Funktion von  $U_{ein}$  und  $U_3$  und dann  $U_2$  als Funktion von  $U_{ein}$  und  $U_3$  an.

- b) Stellen Sie nun eine Knotengleichung für den Knoten 3 auf. Setzen Sie das Ergebnis aus b) 6 ein und entwickeln Sie daraus einen Ausdruck für I<sub>I</sub>.

- c) Geben Sie die Abgleichbedingung an, die erfüllt sein muss, damit  $I_L$  nur eine Funktion der Eingangsspannung  $U_{ein}$  ist und geben Sie die Beziehung zwischen  $I_L$  und  $U_{ein}$  an, die in diesem Falle erhalten wird.

- d) Im Folgenden sollen  $R_L = 2 \text{ k}\Omega$  sein und  $I_L / U_{ein} = 1 \text{ mA} / \text{V}$  gelten. Ferner wird  $R_2 = 2 \text{ k}\Omega$  vorgegeben. Dimensionieren Sie die verbleibenden Widerstände und skizzieren Sie die Spannung, die sich am Knoten 3 für  $U_{ein} = -5 \text{ V} \dots + 5 \text{ V}$  ergibt. Tragen Sie dann in das gleiche Diagramm auch die Spannungen an den Knoten 1 und 2 ein.

Summe: 20

Abbildung zu Aufgabe 4

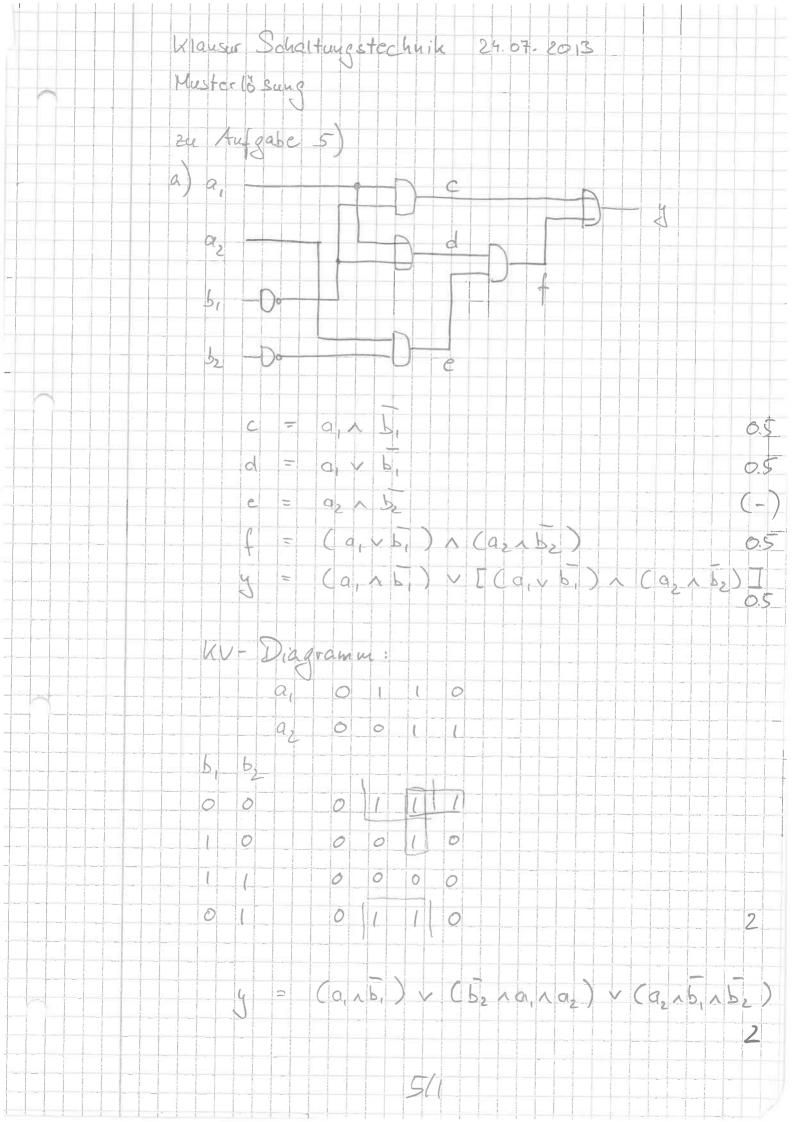

### Aufgabe 5:

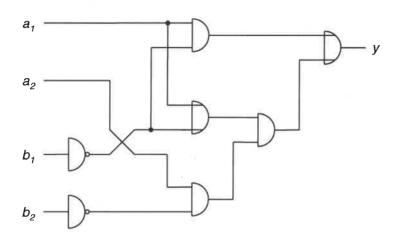

Gegeben ist die unten skizzierte Logik-Schaltung.

- a) Stellen Sie für die Schaltung ein KV-Diagramm auf und bestimmen Sie daraus den logischen 6

Ausdruck für y in möglichst einfacher Form.

- Nehmen Sie an, die skizzierte Schaltung wird mit Hilfe von Standard-CMOS-Logik umgesetzt.

Geben Sie die Anzahl der Transistoren an, die Ihre Schaltung benötigt.

Summe: 10

Abbildung zu Aufgabe 5

d) Gou, u ( Uera = 0) = Gou, p ( Uera = Upo) => Wp = Wn (Cloo-Clona) Kp (Cloo-Cloo) = 1.0 mm 86 1.8-0.7 = 2.933 mm ~ 2.9 eun 116

Mouseur Solattungstechnik 24, 37.2013 Muster 18 suge Zu Aufgabe 3) a) Tu Tiz, 713: Strom Spiegel 121, 722 | P21, 122 (mit Tiz als Strongwelle): Differentstate unit p-1705 Erypongstr. O.S Ohmschen Last eleculeuten 0.5 und diff. Ausgaug 0.5 131,732, R31, R32 (wit 1,3 als Strom guelle): clifo 6)  $R_{21}$   $R_{22}$   $R_{31}$   $R_{32}$ c) I, = = 1 KP UGER 2 - 12.5 pt -0.7 pm 56 mt (025V)2

Wayser Schalfungstechnik 24.07.2018 Muster 18 sung f) Gor, eru, max: Chipt Clark & dl -> Clenen war = UDD - (Clap + 2 ch of) = 3.3 V - (0.7 V + 2.0.25 V)= 2.1 V Gerrera, min : Utup + Class Foll 2 UGett => ((creen, min = 105V + (Geff + (CH, p + Class) 1 = 15V+0.25V-(07V+0.25V)  $= 0.8 \vee$ 3/3

Wayser Schalfrendstechnik 24.67.2013 Muster là sung 9) Befrachte zowiechst 2.B wur die Stufe 1,2, 12, 122, 1221, 222; 2 hein B REDEL BA - 2 hein andert Belitung gue hier Korreht wit guzi = Smez = guz S0221 = S0222 = S022 R21 = R22 = R2 Da 4,0 = 0 1st der Common - Source -Knoten virtuelle Masse 1840 1800 2 Suz year - 2 Suz hein 314

Mausicer Schaltung Stochuck 24.07.2018 Muster Coscue Wrude dieses Erechuis auf gesante Sdalterup au: - 2 acq 8 2 ven 8 420 Sm3 18 0 42 303 18 5023 23 PAS 4 Lp Gaeff 7-5 56 414 · 0,25 V 150 MA/V guz Rz (50 MA/V - 80 MAZ = Sm2 - 3 - R2 - 3 = Sm2 R2 = 12 Sm 3 P3 = 122 = =7 Ago = 144

|    | lausur Schaltungstechnik 24,67.2013<br>luster 15 sung                                   |

|----|-----------------------------------------------------------------------------------------|

|    | Angaben zur Vergabe der bish. Punkte:                                                   |

|    | Gleichungen für C, d, nicht erfordelich,<br>ergeben jedoch Punkte, falls Fehler im      |

|    | Diagramm:  1 Febler - 0.5, d.4. 15 Punkte                                               |

|    | 2 Fehler - 1.0, cl.h. 1.0 Punkte  3 Fehler - 1.5, d.h D.5 Punkte  > 3 Fehler - 0 Punkte |

|    | Identifizierung der Gruppen innerhalb  des Diagramms ist Bestandteil der                |

|    | 1etzten 2 Punkte, d.h. Angabe von y=                                                    |

| 5) | 2 Inverter: 2.2 = 4   1<br>3 ANDS = 3 (NAND + Inverter)   3<br>3 (4+2) = 3.6 = 18   1   |

|    | 2 OR = 2 (NOR + TWOCK + CF)  2 (4+2) = 2 6 = 12 1                                       |

|    | Scrume: (12+18+4) Transistorey = 34 Transistorey                                        |

|    | Augabe der (korrehten) Summe ergibt<br>bereits volle Punktracht                         |

|    | 5/2                                                                                     |