### Aufgabe 1: MIPS Assemblersprache

Übersetzen Sie die folgende Funktion nach MIPS-Assembler.

Beachten Sie dabei die MIPS-Register Konventionen. Pseudo-Instruktionen dürfen verwendet werden.

```

void clip(int a[], int n)

{

int i;

for (i=0; i<n; i++) {

if (a[i]<0)

a[i]=0;

else if (a[i]>255)

a[i] = 255;

}

}

}

```

TochGL-2 Rochmororganication

#### Aufgabe 2: Zahlendarstellungen

- Stellen Sie die Dezimalzahl –87 als 8-Bit 2-Komplement-Zahl dar.

- Stellen Sie die Zahl 10,25 in binärer Darstellung nach IEEE 754 mit einfacher Genauigkeit dar.

TechGI-2, Rechnerorganisation

# Aufgabe 2: Lösungsblatt

- Stellen Sie die Dezimalzahl –87 als 8-Bit 2-Komplement-Zahl dar.

- Stellen Sie die Zahl 10,25 in binärer Darstellung nach IEEE 754 mit einfacher Genauigkeit dar.

TechGI-2, Rechnerorganisation

### Aufgabe 3. Prozessorleistung

Drei Programme (P1, P2 und P3) werden auf zwei verschiedenen Computern (M1 und M2) ausgeführt. Die folgende Tabelle zeigt die Ausführungszeiten beider Programme auf den beiden Computern.

|    | M1  | M2 |

|----|-----|----|

| P1 | 1   | 10 |

| P2 | 100 | 10 |

| P3 | 10  | 5  |

- a) Welches System ist schneller wenn die Ausführungszeit auf M1 normiert wird und der arithmetisch Mittelwert verwendet wird? Begründen Sie ihre Antwort.

- b) Welches System ist schneller wenn die Ausführungszeit auf M2 normiert wird und der arithmetisch Mittelwert verwendet wird? Begründen Sie ihre Antwort.

- c) Welches System ist schneller wenn der geometrische Mittelwert verwendet wird. Begründen Sie Ihre Antwort.

TechGI-2, Rechnerorganisation

### Aufgabe 3. Lösungsblatt

a) Welches System ist schneller wenn die Ausführungszeit auf M1 normiert wird und der arithmetische Mittelwert verwendet wird? Begründen Sie ihre Antwort.

|    | M1  | M2 |

|----|-----|----|

| P1 | 1   | 10 |

| P2 | 100 | 10 |

| P3 | 10  | 5  |

|                             | M1 | M2 |

|-----------------------------|----|----|

| P1                          |    |    |

| P2                          |    |    |

| P3                          |    |    |

| arithmetische<br>Mittelwert |    |    |

TechGI-2, Rechnerorganisation

### Aufgabe 3. Lösungsblatt

b) Welches System ist schneller wenn die Ausführungszeit auf M2 normiert wird und der arithmetische Mittelwert verwendet wird?

Begründen Sie ihre Antwort.

|    | M1  | M2 |

|----|-----|----|

| P1 | 1   | 10 |

| P2 | 100 | 10 |

| P3 | 10  | 5  |

|                             | M1 | M2 |

|-----------------------------|----|----|

| P1                          |    |    |

| P2                          |    |    |

| Р3                          |    |    |

| arithmetische<br>Mittelwert |    |    |

TochGL-2 Bochmororganicatio

### Aufgabe 3. Lösungsblatt

c) Welches System ist schneller wenn der geometrische Mittelwert verwendet wird. Begründen Sie Ihre Antwort.

|                            | M1 | M2 |

|----------------------------|----|----|

| P1                         |    |    |

| P2                         |    |    |

| P3                         |    |    |

| geometrische<br>Mittelwert |    |    |

|                            | M1 | M2 |

|----------------------------|----|----|

| P1                         |    |    |

| P2                         |    |    |

| Р3                         |    |    |

| geometrische<br>Mittelwert |    |    |

TechGI-2, Rechnerorganisation

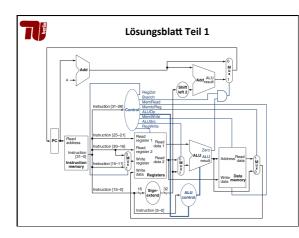

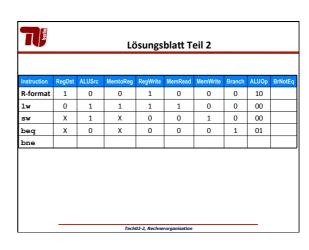

### Aufgabe 4. Der Eintaktprozessor

- Wir möchten den Eintaktprozessor um den Befehl **bne** (branch not equal) erweitern.

- Ergänzen Sie benötigte Datenpfade und Steuersignale in der Abbildung auf der nächsten Folie

- Geben Sie die Werte an, die die Steuersignale haben müssen, so dass der Datenpfad den bne-Befehl ausführt. Verwenden Sie falls möglich Don't Cares.

TechGI-2, Rechnerorganisation

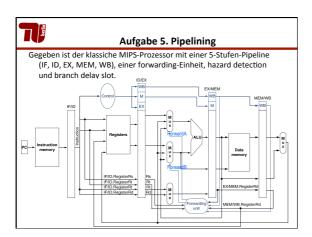

# Aufgabe 5. Pipelining (cont' d)

Die folgende Tabelle zeigt die Quell-/Ziel-Register der Befehle in der EX, MEM und WB Stufe (z.B. ID/EX.Rs ist die Abkürzung für ID/ EX.RegisterRs). Vervollständigen Sie die Tabelle:

| ID/EX.Rs | ID/EX.Rt | EX/MEM.Rd | EX/Mem.RegWrite | MEM/WB.Rd | MEM/WB.RegWrite | ForwardA | ForwardB |

|----------|----------|-----------|-----------------|-----------|-----------------|----------|----------|

| 6        | 7        | 7         | 0               | 8         | 1               |          |          |

| 6        | 7        | 6         | 1               | 7         | 1               |          |          |

| 6        | 7        | 6         | 1               | 6         | 1               |          |          |

| 6        | 0        | 0         | 1               | 6         | 0               |          |          |

TochGL-2 Backmararanicatio

# Aufgabe 6. Caches

- Der AMD Athlon 64 Prozessor Befehlscache auf erster Ebene hat folgende Eigenschaften:

- Kapazität: 64 KB

- > 2-fach satzassoziativ

- ➤ Blockgröße: 64 Bytes

- ➤ Adresslänge: 64 Bit

- Wie groß ist der Index und wie groß ist der Tag?

- Auf welchem Satz wird Byteadresse 64132 abgebildet? Geben Sie den Index an.

TechGI-2, Rechnerorganisation